### The University of Texas at Arlington

### Lecture 2 PIC Overview

### CSE 3442/5442 Embedded Systems I

Based heavily on slides by Dr. Gergely Záruba and Dr. Roger Walker

# **Overview of PIC18 Family**

- Microchip Technology Inc. (1989)

- Introduced microcontrollers called PIC

- Peripheral Interface Controller

- 8-bit MCUs

- PIC10, PIC12, PIC16, PIC18

- -16-bit MCUs

- PIC24

- -32-bit MCUs

- PIC32

-www.Microchip.com

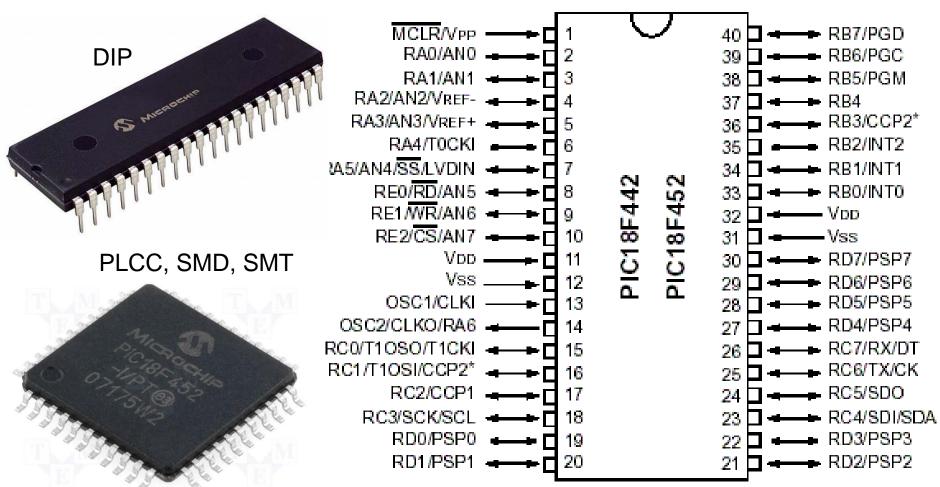

### **PIC18F452**

### Datasheet Link

- https://www.microchip.com/wwwproducts/en/en010296

- Or

- <u>http://omega.uta.edu/~nbb0130/misc\_files/PIC18FXX2%20Data</u>

<u>%20Sheet.pdf</u>

#### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

• PIC18F242 • PIC18F442

**TABLE 1-1:**

• PIC18F252 • PIC18F452

These devices come in 28-pin and 40/44-pin packages. The 28-pin devices do not have a Parallel Slave Port (PSP) implemented and the number of Analog-to-Digital (A/D) converter input channels is reduced to 5. An overview of features is shown in Table 1-1.

DEVICE FEATURES

# The following two figures are device block diagrams sorted by pin count: 28-pin for Figure 1-1 and 40/44-pin for Figure 1-2. The 28-pin and 40/44-pin pinouts are listed in Table 1-2 and Table 1-3, respectively.

| Features                      | PIC18F242   | PIC18F252   | PIC18F442   | PIC18F452   |

|-------------------------------|-------------|-------------|-------------|-------------|

| Operating Frequency           | DC - 40 MHz |

| Program Memory (Bytes)        | 16K         | 32K         | 16K         | 32K         |

| Program Memory (Instructions) | 8192        | 16384       | 8192        | 16384       |

| Data Memory (Bytes)           | 768         | 1536        | 768         | 1536        |

| D-1- EEDDOM M                 | 050         | 050         | 050         | 050         |

# **8-bit Microchip Families**

- Microchip is one of the main suppliers of 8-bit microcontrollers

- PIC families include 10xxx, 12xxx,14xxx, 16xxx, 17xxx, and 18xxx

- 12xxx/16xxx have 12-bit & 14-bit instructions

- PIC18xxx have 16-bit instructions

- Mouser Link

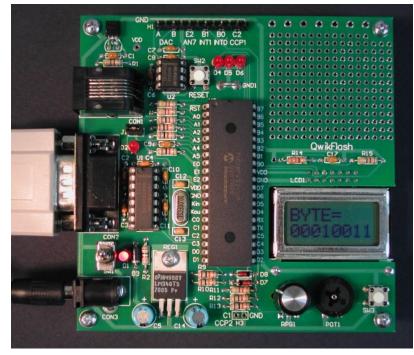

# QwikFlash (Kit Used in Lab)

- QwikFlash Development Kit No. 3

- Expanded Kit with breadboard 400 and Stand

- <u>http://www.microdesignsinc.com/qwikflash/index.htm</u>

- http://www.microdesignsinc.com/picbook/

- Schematic Link

### **QwikFlash**

- ROM program or code ROM

- PIC18 can have up to 2 megabytes (2M) of ROM

- UV-EPROM for program memory

– must have special eraser/programmer (burner ~20 minutes to erase)

- Flash memory PIC18<u>F</u>458 use for program development, can reprogram again and again

- OTP Version PIC16<u>C</u>452 use for final production version, one time programmable (ROM)

- **EEPROM** electrically erasable PROM, additional "permanent" memory

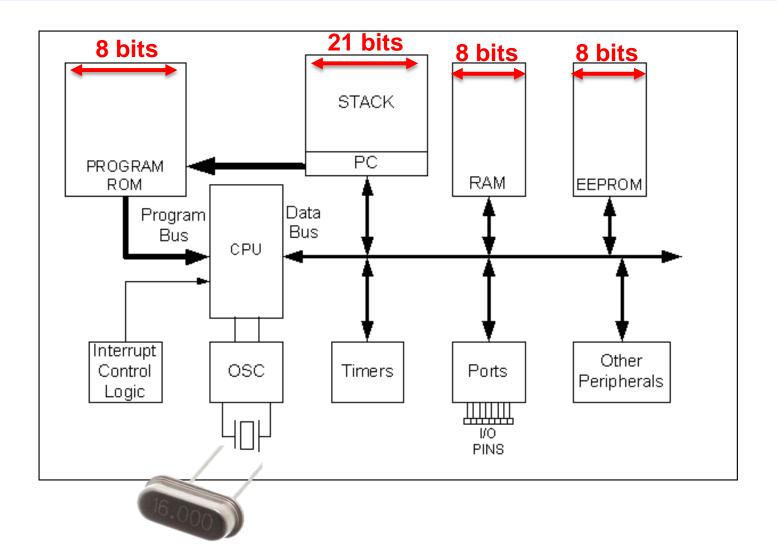

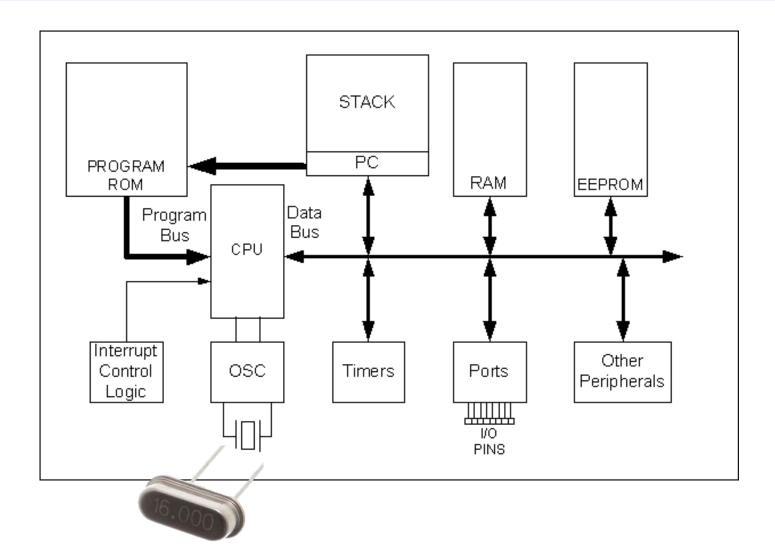

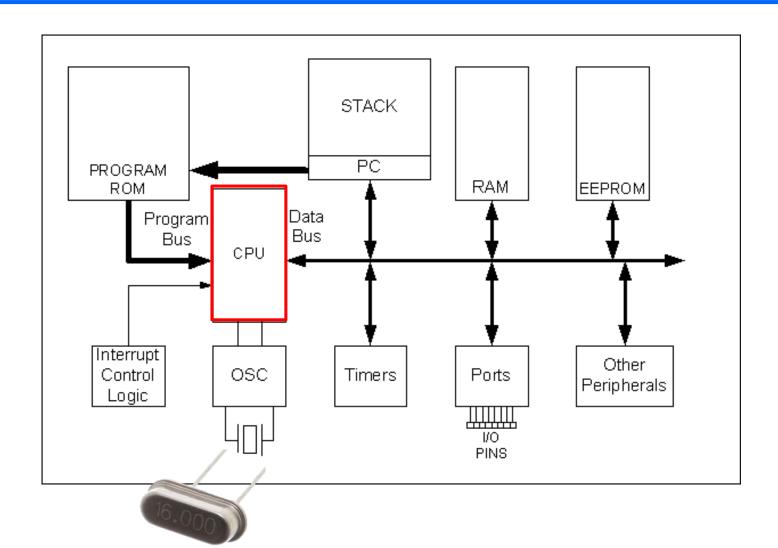

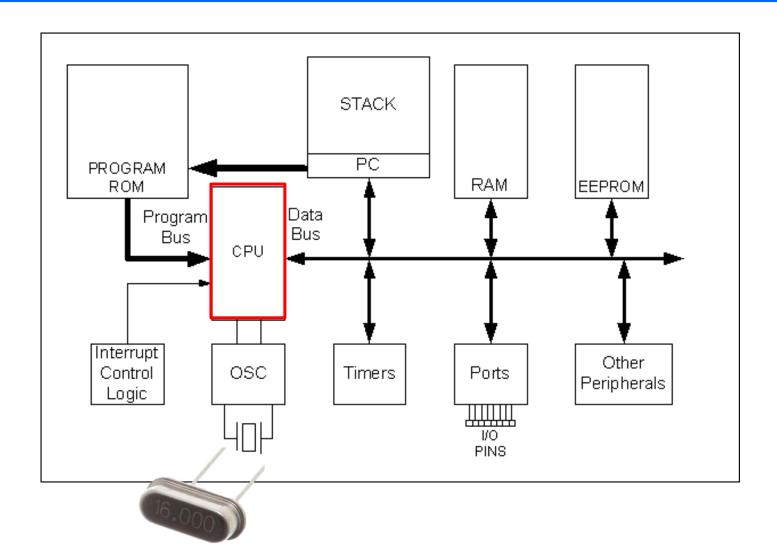

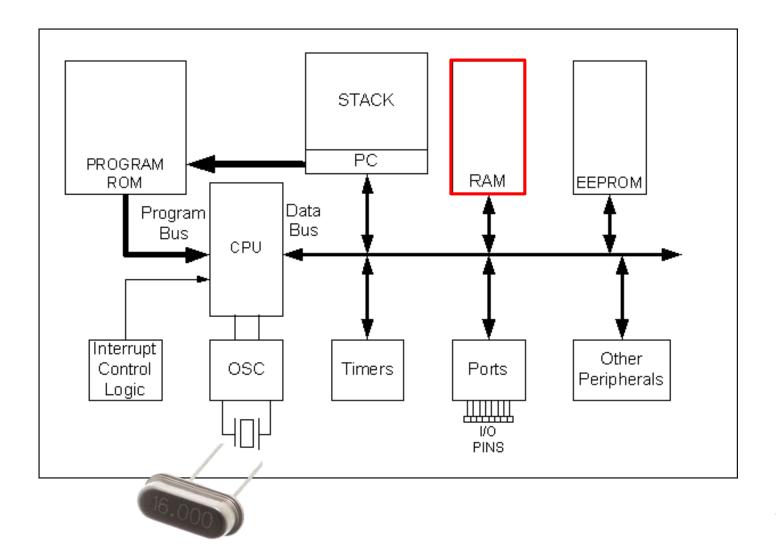

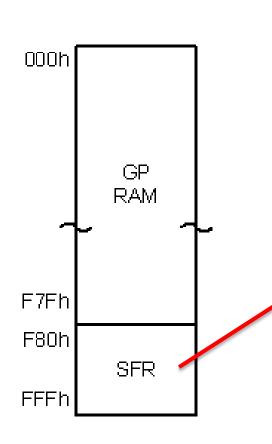

### Simplified View of a PIC Microcontroller

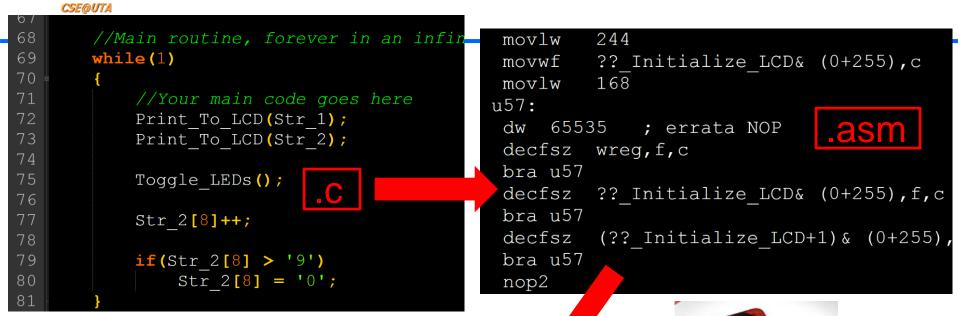

# **Software Program Flow**

# **Programming a PIC**

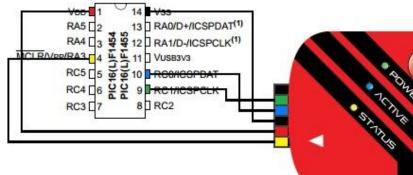

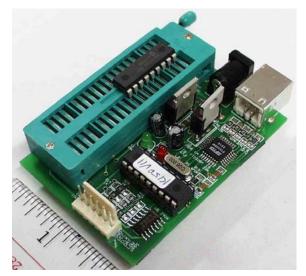

### • PicKit 3 (ICSP)

Socket

Programmer

Microchip Tecnology Inc.

# **Software Program Flow**

:100760000FEC03F01200FFFFFFF9EEC03F0 :10077000156E060E166E57EC03F0010E156E060E82 :10078000166E57EC03F0FFFFED7C02020202020207C :10079000202020008020202020202020202000FFFF7B :02000040020DA :08000000FFFFFFFFFFFFFFFFFF00 :020000040030CA :0E000000FF220D0EFF0181FF0FC00FE00F4029 :0000001FF

- PIC18 one of the higher performers of the Microchip's PIC families. There is now both a 32 bit PIC32 family and DSPIC (16 bit) with high performance.

- PIC families come in 18 to 80 pin packages.

- Select family based on performance, footprint, etc., needed, use selection guide: <u>http://www.microchip.com/stellent/idcplg?IdcSer</u> <u>vice=SS\_GET\_PAGE&nodeId=2661</u>

- RISC architecture

- On-chip program ROM, data RAM, data EEPROM, timers, ADC, USART, and I/O Ports

• ROM, data RAM, data EEPROM, and I/O ports sizes varies within PIC18 family

### Simplified View of a PIC Microcontroller

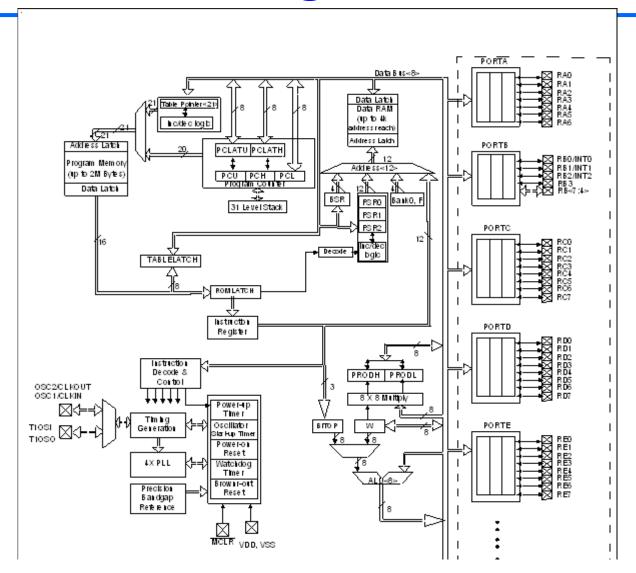

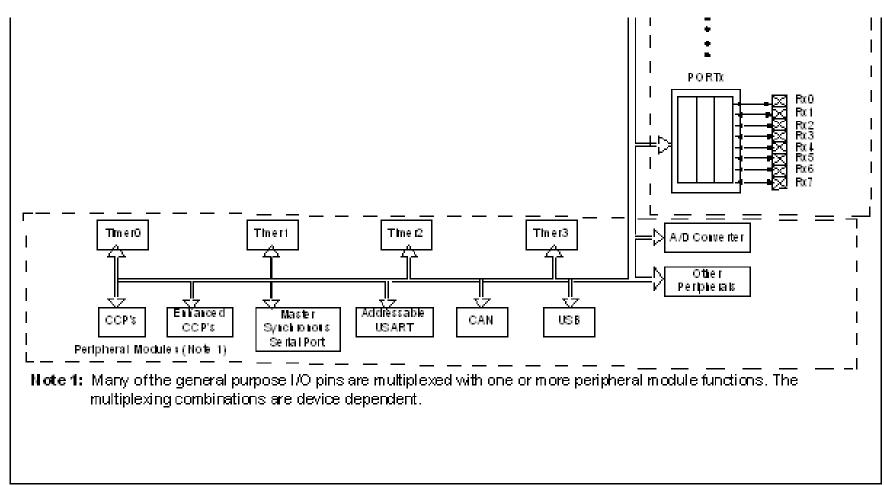

## Figure 1-3. PIC18 Block Diagram

16

# Figure 1-3. PIC18 Block Diagram (continued)

# What is a **Register**?

### Register

### A place inside the PIC that can be written to, read from, or both (8-bit numbers)

#### TABLE 9-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name    | Bit 7                         | Bit 6         | Bit 5   | Bit 4   | Bit 3  | Bit 2     | Bit 1     | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|---------|-------------------------------|---------------|---------|---------|--------|-----------|-----------|--------|----------------------|---------------------------------|

| PORTB   | RB7                           | RB6           | RB5     | RB4     | RB3    | RB2       | RB1       | RB0    | xxxx xxxx            | uuuu uuuu                       |

| LATB    | LATB Data Output Register     |               |         |         |        | xxxx xxxx | uuuu uuuu |        |                      |                                 |

| TRISB   | PORTB Data Direction Register |               |         |         |        | 1111 1111 | 1111 1111 |        |                      |                                 |

| INTCON  | GIE/<br>GIEH                  | PEIE/<br>GIEL | TMR0IE  | INTOIE  | RBIE   | TMR0IF    | INTOIF    | RBIF   | 0000 000x            | 0000 000u                       |

| INTCON2 | RBPU                          | INTEDG0       | INTEDG1 | INTEDG2 | _      | TMR0IP    | —         | RBIP   | 1111 -1-1            | 1111 -1-1                       |

| INTCON3 | INT2IP                        | INT1IP        | _       | INT2IE  | INT1IE | _         | INT2IF    | INT1IF | 11-0 0-00            | 11-0 0-00                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

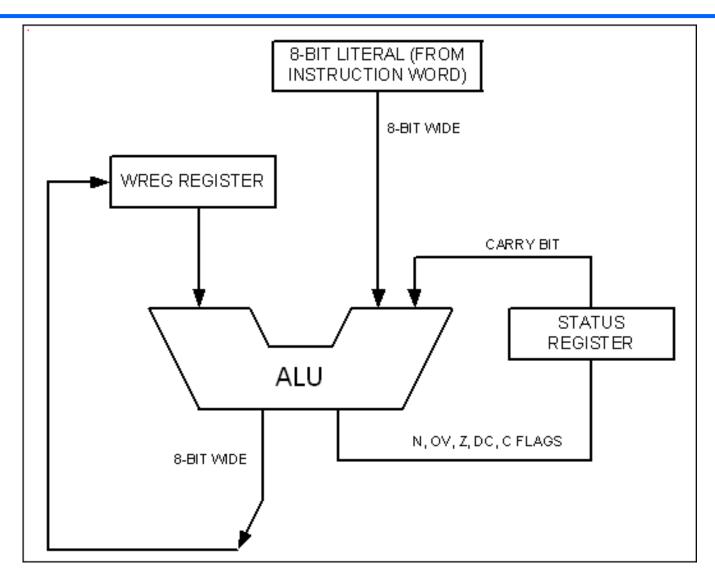

- <u>Working Reg</u>ister is the same as the accumulator in other microprocessors

- Used for all arithmetic/logic instructions

- Avoids use of main memory

- Close as possible to the ALU within the CPU

- Can only hold 0-255 dec (0-FFh)

- Truncates larger values and causes warning

- 1001 1101 1100 = 2,524dec = 9DCh

- 0000 1101 1100 = 220dec = DCh

### WREG is in the CPU

Ch. 2 - PIC Architecture & Assembly Language Programming

WREG – 8 bit register in PIC (Working Register) – used for most instructions

MOVLW K

Move ("MOV") the number ("L" for "literal") K into the working register ("W")

### MOVLW 0xA

That is, load W with the value 0xA Note: 'WREG' sometimes shortened to 'W'

- MOVLW K; move literal value K into WREG

- Once again K is an 8 value 0-255 decimal or 00-FF in hex

Ex.

MOVLW 25H; move 25H (0x25) into WREG (WREG = 25H)

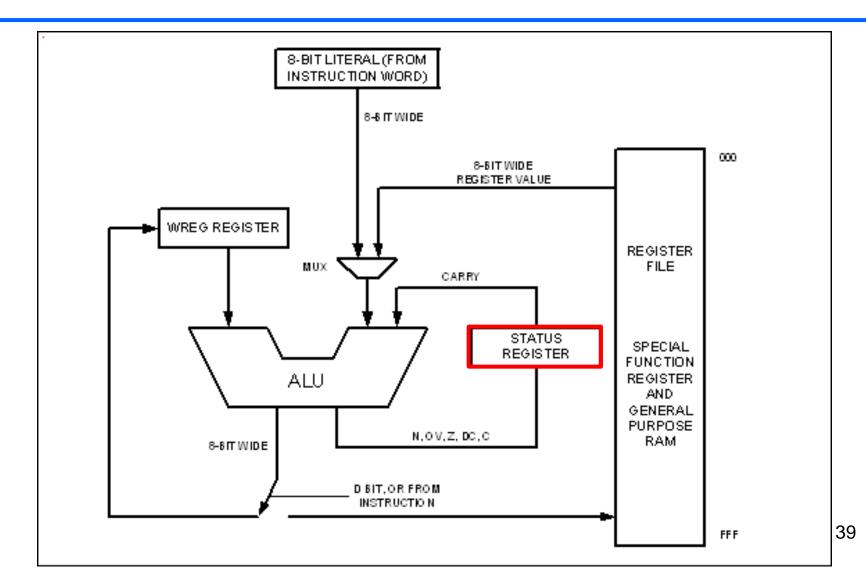

# **ALU is in the CPU**

## PIC WREG and ALU Using Literal Value

24

## **Move and Add Instructions**

- MOVLW 12H

- ADDLW 16H

- ADDLW 11H

- ADDLW 43H

;load value 12H -> WREG ;add 16H to WREG ;add 11H to WREG ;add 43H to WREG

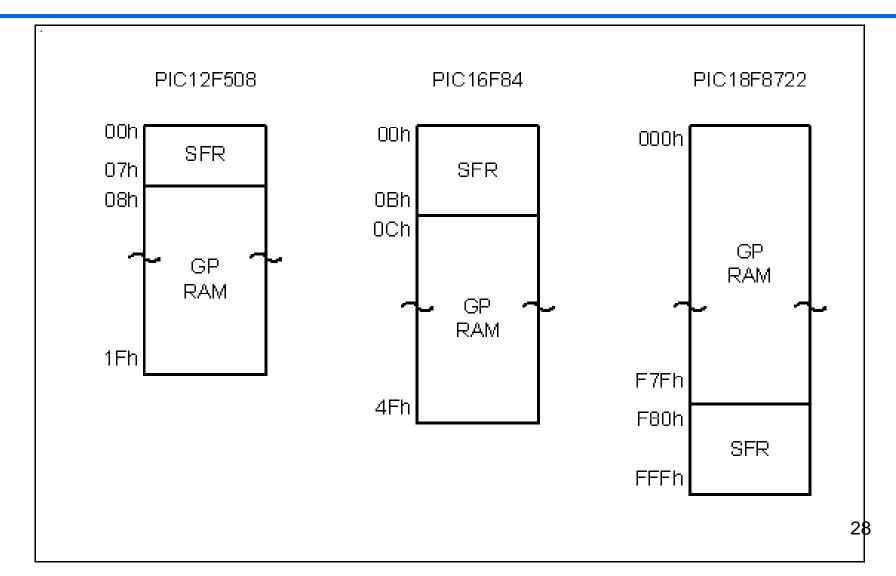

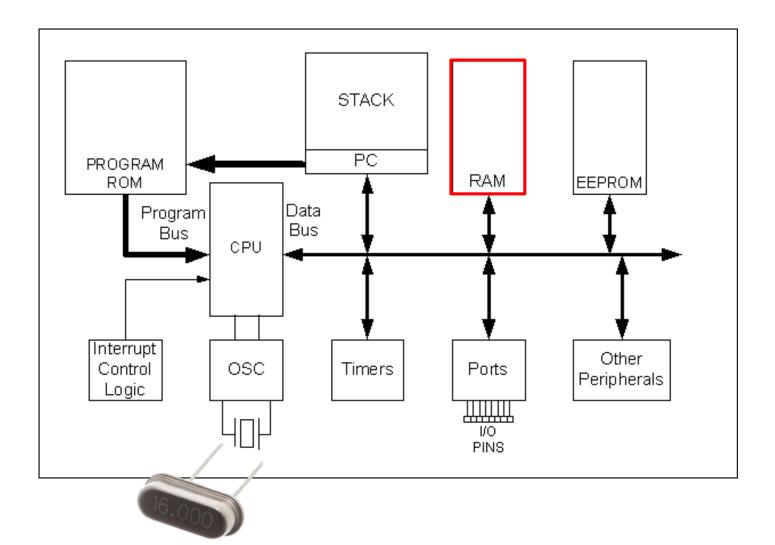

# **FILE REGISTER**

### • File Register = Data Memory (RAM)

- Read/write memory used by CPU for data storage

- Varies from 32 bytes to thousands depending on chip size (family)

- Can perform arithmetic/logic operations on many locations of File Register data

- Divided into two sections:

- Special Function Registers (SFR)

- General Purpose Registers (GPR) or (GP RAM)

# File Registers of PIC12, PIC16, and PIC18

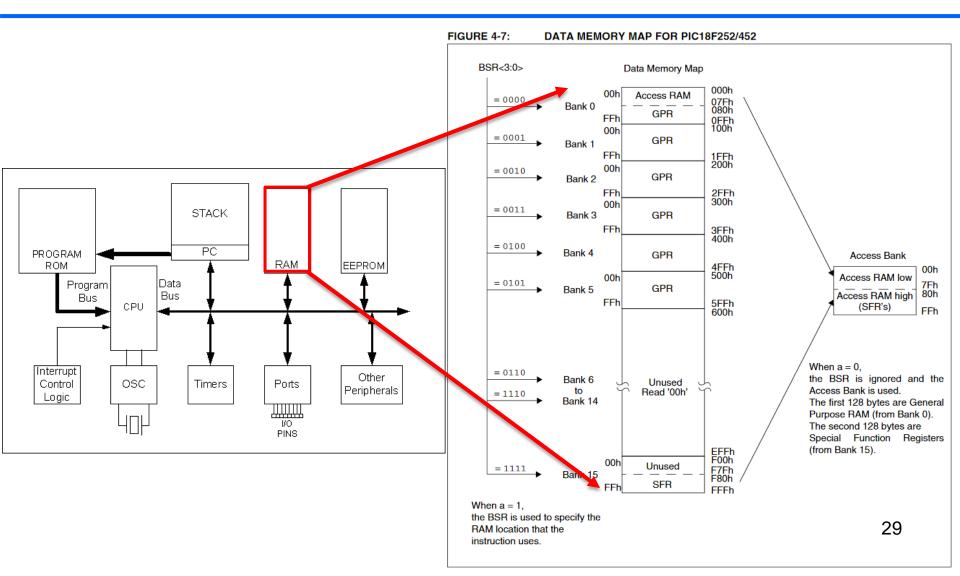

### File Register (Data RAM) for the PIC18F452

# FILE REGISTER cont.

### • SFR – special functions (8-bit wide regs)

- Functionality of each is fixed in design

- Usually for all of the peripherals

- ALU status

- Timers

- Ex: the more timers the more SFR in a PIC

- Serial communications

- I/O Ports

- A/D

### Special Function Registers of the PIC18 Family

| F80h | PORTA |

|------|-------|

| F81h | PORTB |

| F82h | PORTC |

| F83h | PORTD |

| F84h | PORTE |

| F85h |       |

| F86h |       |

| F87h |       |

| F88h |       |

| F89h | LATA  |

| F8Ah | LATB  |

| F8Bh | LATC  |

| F8Ch | LATD  |

| F8Dh | LATE  |

| F8Eh |       |

| F8Fh |       |

| F90h |       |

| F91h |       |

| F92h | TRISA |

| F93h | TRISB |

| F94h | TRISC |

| F95h | TRISD |

| F96h | TRISE |

| F97h |       |

| F98h |       |

| F99h |       |

| F9Ah |       |

| F9Bh |       |

| F9Ch |       |

| F9Dh | PIE1  |

| F9Eh | PIR1  |

| F9Fh | IPR1  |

|      |       |

| FAOh   | PIE2     |

|--------|----------|

| FA1h   | PIR2     |

| F A2h  | IPR2     |

| FA3h   |          |

| F A4h  |          |

| FAGh   |          |

| FA6h   |          |

| FA7h   |          |

| F A8h  |          |

| FA9h   |          |

| FAAh   |          |

| FABh   | RCSTA    |

| FACh   | TXSTA    |

| FADh   | TXREG    |

| FAEh   | RCREG    |

| FAFh   | SPBRG    |

| FBOh   |          |

| FB1h   | T3C ON   |

| FB2h   | TMR3L    |

| FB3h   | тмrзн    |

| F B4h  |          |

| F B5h  |          |

| F B6h  |          |

| F 87 h |          |

| F B8h  |          |

| F B9h  |          |

| FBAh   | CCP2CON  |

| FBBh   | CCPR2L   |

| FBCh   | CC PR2H  |

| FBDh   | CCP1CON  |

| FBEh   | CCPR1L   |

| FBFh   | CC PR 1H |

|        |          |

| FCOh  |          |

|-------|----------|

| FC1h  | ADC ON1  |

| FC2h  | ADCONO   |

| FСЗh  | ADRESL   |

| FC4h  | ADRESH   |

| F C5h | SSPC ON2 |

| F C6h | SSPC ON1 |

| FC7h  | SSPSTAT  |

| F C8h | SSPADD   |

| F C9h | SSPBUF   |

| FCAh  | T2CON    |

| FCBh  | PR2      |

| FCCh  | TMR2     |

| FCDh  | T1CON    |

| FCEh  | TMR 1L   |

| FCFh  | TMR1H    |

| FDOh  | RCON     |

| FD1h  | WDTCON   |

| F D2h | LVDCON   |

| FDЗh  | OSCCON   |

| F D4h |          |

| FD5h  | TOCON    |

| FD6h  | TMROL    |

| FD7h  | TMROH    |

| F D8h | STATUS   |

| F D9h | FSR2L    |

| FDAh  | FSR2H    |

| FDBh  | PLUSW2   |

| FDCh  | PREINC2  |

| FDDh  | POSTDEC2 |

| FDEh  | POSTINC2 |

| FDFh  | IN DF2   |

|       |          |

| FEOh  | BSR      |   |

|-------|----------|---|

| FE1h  | FSR1L    |   |

| FE2h  | F SR 1H  |   |

| FE3h  | PLUSW1   | ~ |

| FE4h  | PREINC1  | ~ |

| FE5h  | POSTDEC1 | * |

| FE6h  | POSTINC1 | ~ |

| FE7h  | IND F1   | * |

| FE8h  | WREG     |   |

| FE9h  | FSROL    |   |

| FEAh  | FSROH    |   |

| FEBh  | PLUSWO   | * |

| FECh  | PREINCO  | * |

| FEDh  | POSTDECO | ~ |

| FEEh  | POSTINCO | * |

| FEFh  | IND FO   | ~ |

| F FOh | IN TCON3 |   |

| FF1h  | IN TCON2 |   |

| F F2h | INTCON   |   |

| FFЗh  | PRODL    |   |

| FF4h  | PRODH    |   |

| F F5h | TABLAT   |   |

| F F6h | TBLPTRL  |   |

| FF7h  | TBLPTRH  |   |

| F F8h | TBLPTRU  |   |

| F F9h | PCL      |   |

| FF Ah | PCLATH   |   |

| FFBh  | PCLATU   |   |

| FFCh  | STKPTR   |   |

| FFDh  | TOSL     | Í |

| FFEh  | TOSH     |   |

| FFFh  | TOSU     | Í |

\* - These are not physical registers.

31

# FILE REGISTER – cont.

- **GPR general-purpose** (8-bit wide regs)

- RAM locations used for ANY data storage and scratch pad as long as it's 8 bits (data RAM size same as GFR size)

- Larger GPR = more difficult to manage in ASM

- C compilers now handle management/addressing

- GPR ≠ EEPROM

- GPR used by CPU for "internal" data storage

- EEPROM considered "add-on" memory

# File Registers, cont.

- PIC File Register has max 4K or 000-FFFH

Addresses (locations) are 12-bit wide

- Divided into 16 banks of 256 bytes

- All PIC's have at least one bank...

### – Access Bank

The access bank divided into 2 sections of 128 bytes, SFR and GPR

### PIC18 File Register and Access Bank

- Bank switching required (as only 256 bytes are addressable) in File Registers if using more than 256 bytes:

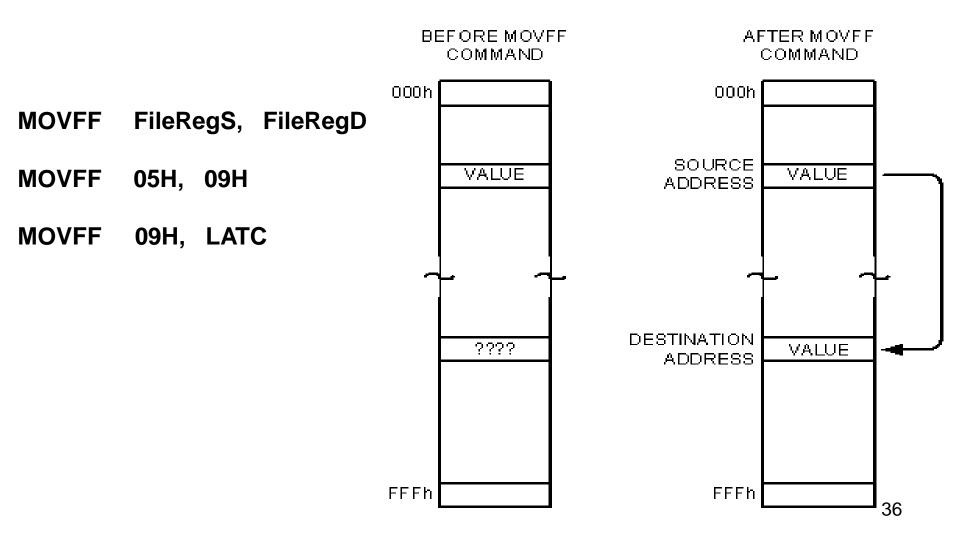

- MOV **WF** used to copy from work register into file register:

- MOVLW 12H ; 12H -> WREG

- MOVWF 16H ; (WREG) -> File Register 16H

- MOVWF PORTC ; (WREG) -> PORTC (F8BH)

### Moving Data Directly Among the fileReg Locations

#### Choosing Location to Store Result

### • **ADDWF fileReg, D**; (D = Destination Bit)

- Contents of WREG added to contents of fileReg address location

- If D = 0, result placed in WREG

- If D = 1, result placed in fileReg location

e.g., **ADDWF 16H, 0**; add the value contained in 16H to the value of W (thus store in W)

e.g., **ADDWF PORTC, 1**; add the value contained in W to the value of PORTC/F82H (thus store in F82H/PORTC's IO Pins)

### Add with CARRY or Not

#### • **ADDWF fileReg, d** ;ADD WREG & fileReg

- $-W + F \rightarrow d$

- If d = 0, result put in WREG

- If d = 1, result put in F (location)

#### • ADDWFC fileReg, d ;ADD WREG & fileReg & Carry

- $-W + F + C \rightarrow d$

- If d = 0, result put in WREG

- If d = 1, result put in F (location)

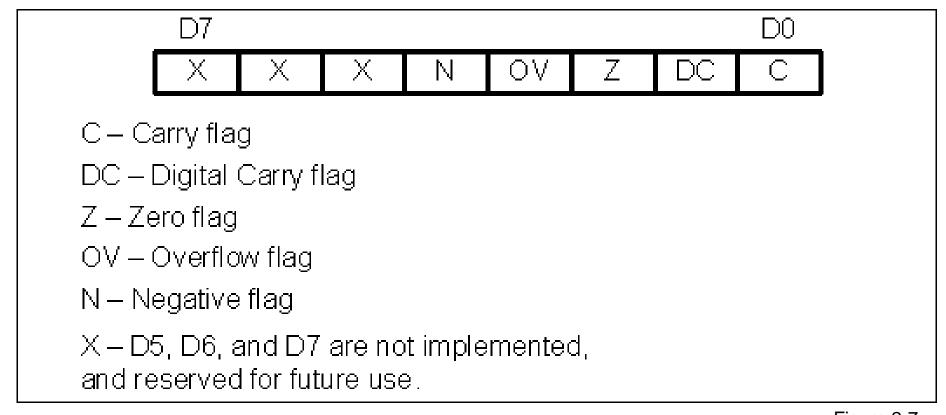

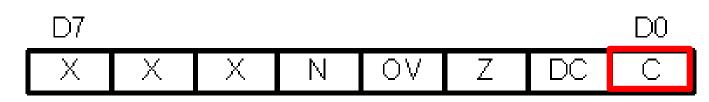

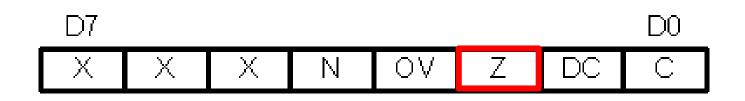

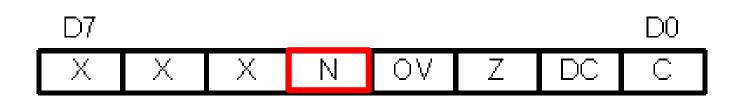

## **Bits of Status Register**

Figure 2-7

- C Flag is set (1) when there is a "carry out" from the D7 bit

- Can be set by an ADD or SUB

- 1101 1010

- + 1010 1111

- =<u>1 1</u>000 1001

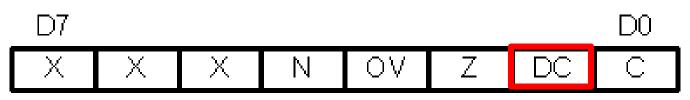

- DC Flag is set (1) when there is a "carry" from the D3 to D4 bits

- Can be set by an ADD or SUB

- 1101 1010

- + 1010 1111

- = 1 100<u>0 1</u>001

- Used by instructions that perform BCD arithmetic

• Z Flag indicates if the the result of an arithmetic or logic operation is 0

- OV Flag is set (1) when the result of a signed number operation is too large

- The numerical result overflows/overtakes the sign bit of the number

- Usually used to detect errors in signed operations

N Flag is set (1) when the result of an arithmetic operation is less than zero

If D7 bit = 0, N = 0, positive result

- If D7 bit = 1, N = 1, negative result

### Flags Affected Following Execution of Most Instructions

- See Table 2-4. on page 60 of textbook

- ADDLW can affect C, DC, Z, OV N

- ANDLW can affect Z

- MOVF can affect Z

- Move instructions (except for MOVF) will not affect any status bits

### **ADDLW Example**

- MOVLW 38H

- ADDLW 2FH

| 38H          | 0011 1000 |            |

|--------------|-----------|------------|

| + <u>2FH</u> | 0010 1111 |            |

| 67H          | 0110 0111 | WREG = 67H |

| C = ?        |           |            |

| DC = ?       |           |            |

| Z = ?        |           |            |

## **ADDLW Example**

- MOVLW 38H

- ADDLW 2FH

- +<u>2FH 0010 1111</u>

- 67H 0110 0111 WREG = 67H

- C = 0 no carry out from bit 7

- DC = 1 carry out from bit 3 to 4

- Z = 0 WREG has value other than zero after addition

## **ADDLW Example cont.**

- MOVLW 9CH

- ADDLW 64H

| 9CH          | 1001 1100            |

|--------------|----------------------|

| + <u>64H</u> | 0110 0100            |

| 100H         | 0000 0000 WREG = 00H |

| C = ?        |                      |

| DC = ?       |                      |

| Z = ?        |                      |

# **ADDLW Example cont.**

- MOVLW 9CH

- ADDLW 64H

| Z = 1        | WREG has value of zero after addition |

|--------------|---------------------------------------|

| DC = 1       | carry out from bit 3 to 4             |

| C = 1        | carry out from bit 7                  |

| 100H         | 0000 0000 WREG = 00H                  |

| + <u>64H</u> | 0110 0100                             |

| 9CH          | 1001 1100                             |

|              |                                       |

- BC

- BNC

- BZ

- BNZ

- BN

- BNN

- BOV

- BNOV

Branch if C = 1 (carry, positive) Branch if  $C \neq 1$ Branch if Z = 1 (zero) Branch if  $Z \neq 1$ Branch if N = 1 (negative) Branch if  $N \neq 1$ Branch if OV = 1 (overflow, 2s cmp) Branch if  $OV \neq 1$

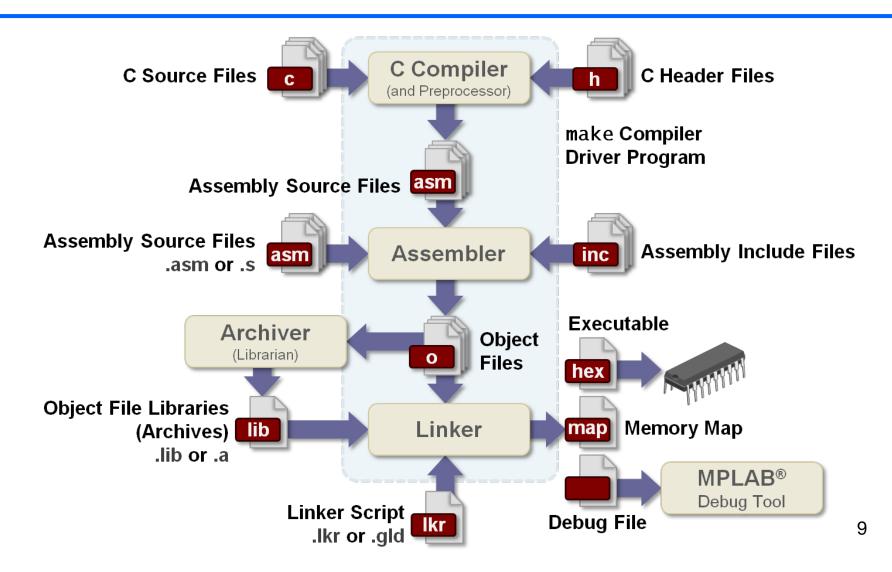

• Read Chapter 0-2 of textbook

### Download:

- MPLAB X IDE (v5.05)

- http://www.microchip.com/mplab/mplab-x-ide

- XC8 Compiler (v2.00)

- <u>http://www.microchip.com/mplab/compilers</u>

Scroll to the bottom of the pages and click the "Downloads" tab. Pick the install for your OS.